IS41LV16100C-50TLI ISSIElectronic Integrated Circuits Dynamic Random Access Memory

1.FEATURES

• TTL compatible inputs and outputs; tristate I/O

• Refresh Interval:

— Auto refresh Mode: 1,024 cycles /16 ms

— RAS-Only, CAS-before-RAS (CBR), and Hidden

— Self refresh Mode: 1,024 cycles /128 ms

• JEDEC standard pinout

• Single power supply:

5V ± 10% (IS41C16100C)

3.3V ± 10% (IS41LV16100C)

• Byte Write and Byte Read operation via two CAS

• Industrial Temperature Range: -40oC to +85oC

2.DESCRIPTION

TheISSIIS41C16100CandIS41LV16100Care1,048,576

x 16-bit high-performance CMOS Dynamic Random Access

Memories. These devices offer a cycle access called

Extended Data Out (EDO) Page Mode. EDO Page Mode

allows 1,024 random accesses within a single row with

access cycle time as short as 30 ns per 16-bit word. It is

asynchronous, as it does not require a clock signal input

to synchronize commands and I/O.

ThesefeaturesmaketheIS41C/41LV16100Cideallysuited

for high-bandwidth graphics, digital signal processing,

high-performance computing systems, and peripheral

applications that run without a clock to synchronize with

the DRAM.

The IS41C/41LV16100C is packaged in a 42-pin 400-mil

SOJ and 400-mil 50/44 pin TSOP (Type II)

3.KEY TIMING PARAMETERS

4.PIN CONFIGURATIONS 50(44)-Pin TSOP (Type II)

5.FUNCTIONAL BLOCK DIAGRAM

6.Functional Description The IS41C/41LV16100C is a CMOS DRAM optimized for high-speed bandwidth, low power applications. During READ or WRITE cycles, each bit is uniquely addressed through the 16 address bits. These are entered ten bits (A0-A9) at time. The row address is latched by the Row Address Strobe (RAS).The column address is latched by the Column Address Strobe (CAS). RAS is used to latch the first nine bits and CAS is used to latch the latter nine bits. The IS41C/41LV16100C has two CAS controls, LCAS and UCAS. The LCAS and UCAS inputs internally generates a CAS signal functioning in an identical manner to the single CAS input on the other 1M x 16 DRAMs. The key difference is that each CAS controls its corresponding I/O tristate logic (in conjunction with OE and WE and RAS). LCAS controls I/ O0 through I/O7 and UCAS controls I/O8 through I/O15. The IS41C/41LV16100C CAS function is determined by the first CAS (LCAS or UCAS) transitioning LOW and the last transitioning back HIGH. The two CAS controls give the IS41C16100C and IS41LV16100C both BYTE READ and BYTE WRITE cycle capabilities. Memory Cycle A memory cycle is initiated by bring RAS LOW and it is terminated by returning both RAS and CAS HIGH. To ensures proper device operation and data integrity any memory cycle,onceinitiated,mustnotbeendedoraborted before the minimum tras time has expired. A new cycle must not be initiated until the minimum precharge time trp, tcp has elapsed. Read Cycle A read cycle is initiated by the falling edge of CAS or OE, whicheveroccurs last,whileholdingWEHIGH.Thecolumn address must be held for a minimum time specified by tar. Data Out becomes valid only when trac, taa, tcac and toea are all satisfied.As a result, the access time is dependent on the timing relationships between these parameters. Write Cycle A write cycle is initiated by the falling edge of CAS and WE, whichever occurs last. The input data must be valid at or beforethefallingedgeofCASorWE,whicheveroccursfirst. Auto Refresh Cycle To retain data, 1,024 refresh cycles are required in each 16 ms period.There are two ways to refresh the memory. 1. By clocking each of the 1,024 row addresses (A0 through A9) with RAS at least once every tref max.Any read, write, read-modify-writeorRAS-onlycyclerefreshestheaddressed row. 2. Using a CAS-before-RAS refresh cycle. CAS-beforeRASrefreshisactivatedby thefallingedgeofRAS,while holding CAS LOW. In CAS-before-RAS refresh cyclean internal 9-bit counter provides the row addresses and the external address inputs are ignored. CAS-before-RAS is a refresh-only mode and no data access or device selection is allowed. Thus, the output remains in the High-Z state during the cycle. Self Refresh Cycle The Self Refresh allows the user a dynamic refresh, data retention mode at the extended refresh period of 128 ms. i.e., 125 µs per row when using distributed CBR refreshes. The feature also allows the user the choice of a fully static, low power data retention mode. The optional Self Refresh feature is initiated by performing a CBR Refresh cycle and holding RAS LOW for the specified tRAS. The Self Refresh mode is terminated by driving RAS HIGH for a minimum time of tRP.This delay allows for the completion of any internal refresh cycles that may be in process at the time of the RAS LOW-to-HIGH transition. If the DRAM controller uses a distributed refresh sequence, a burst refresh is not required upon exiting Self Refresh. However,iftheDRAMcontrollerutilizesaRAS-onlyorburst refresh sequence, all 1,024 rows must be refreshed within the average internal refresh rate, prior to the resumption of normal operation. Extended Data Out Page Mode EDO page mode operation permits all 1,024 columns within a selected row to be randomly accessed at a high data rate. In EDO page mode read cycle, the data-out is held to the next CAS cycle’s falling edge, instead of the rising edge. For this reason, the valid data output time in EDO page mode is extended compared with the fast page mode. In the fast page mode, the valid data output time becomes shorter as the CAS cycle time becomes shorter. Therefore, in EDO page mode, the timing margin in read cycle is larger than that of the fast page mode even if the CAS cycle time becomes shorter. In EDO page mode, due to the extended data function, the CAS cycle time can be shorter than in the fast page mode if the timing margin is the same. TheEDOpagemodeallowsbothreadandwriteoperations during one RAS cycle, but the performance is equivalent to that of the fast page mode in that case. Power-On During Power-On, RAS, UCAS, LCAS, and WE must all track with Vdd (HIGH) to avoid current surges, and allow initialization to continue. An initial pause of 200 µs is required followed by a minimum of eight initialization cycles (any combination of cycles containing a RAS signal).

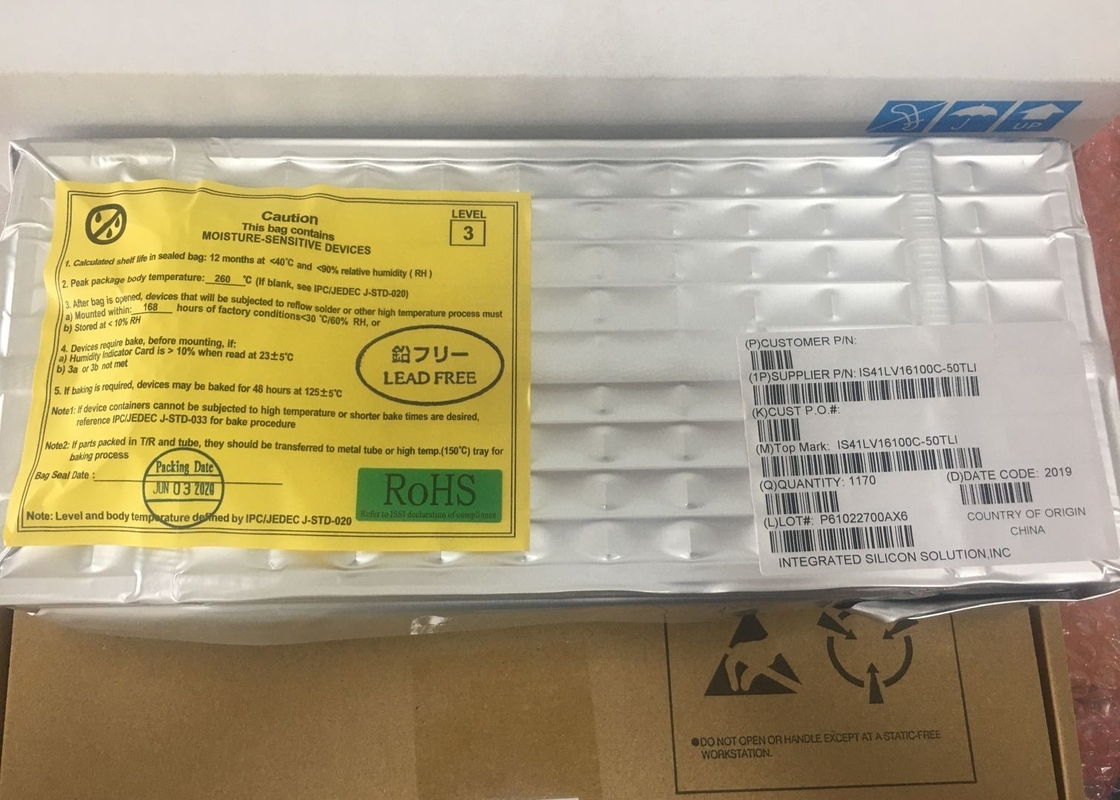

Q1. What is your terms of packing?

A: Generally, we pack our goods in neutral white boxes and brown cartons.

If you have legally registered patent, we can pack the goods in your branded boxes after getting your authorization letters.

Q2. What is your MOQ?

A: We provide you small MOQ for each item, it depends your specific order!

Q3. Do you test or check all your goods before delivery?

A: Yes, we have 100% test and check all goods before delivery.

Q4: How do you make our business long-term and good relationship?

We keep good quality and competitive price to ensure our customers benefit ;

We respect every customer as our friend and we sincerely do business and make friends with them,It's not something that can be replaced.

Q5: How to contact us?

A: Send your inquiry details in the below,Click "Send"Now!!!

Shenzhen Hongxinwei Technology Co., Ltd

To adopt new technology,to produce products of quality,to offer high-class service.

Improve the management system continuously to meet customer requirement for high-quality products and services.

Why choose us?

- 100% new and originao with Advantage price

- High efficiency

- Fast Delivery

- Professional team service

- 10 Years Experience Electronic components

- Electronic components Agent

- Advantage logistic discount

- Excellent After-sales Service

Your message must be between 20-3,000 characters!

Your message must be between 20-3,000 characters! Please check your E-mail!

Please check your E-mail!  Your message must be between 20-3,000 characters!

Your message must be between 20-3,000 characters! Please check your E-mail!

Please check your E-mail!